“信号跳变抵达窗口”:对latch寄存器来说,从previous时钟对应的Hold Time开始,到current时钟对应的Setup Time结束。

“信号电平采样窗口”:对latch寄存器来说,从current时钟对应的 Setup Time 开始,到current时钟对应的Hold Time结束。

launch寄存器必须保证驱动的信号跳变到达latch寄存器的时刻处于“信号跳变抵达窗口”内,才能保证不破坏latch寄存器的“信号电平采样窗口”。

不设置多周期的后果有两个:一是虚报时序违规,二是造成过约束,占用布局布线资源。

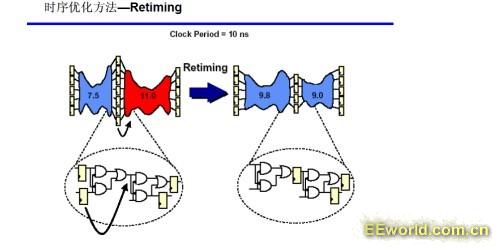

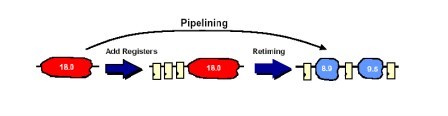

关键路径通常是指同步逻辑电路中组合逻辑延时最大的路径。常用的时序优化方法包括pipeline(增加寄存器)、tetiming两种。

FPGA时序约束的几种方法

(0)主频率约束

(1)主频率约束+时序例外约束

时序例外约束包括false path,multicycle path,max delay,min delay。

(2)主频率约束+时序例外约束+IO约束

IO约束包括引脚分配位置,空闲引脚驱动方式,外部走线延时,上下拉电阻,驱动电流强度等。

正因为FPGA的IO timing会在设计期间发生变化,所以准确的对其进行约束时保证设计稳定可靠地重要因素。许多FPGA重新编译后,FPGA对外部器件的操作出现不稳定的问题都有可能是由此引起。

(3)主频率约束+时序例外约束+IO约束+增量编译

增量编译属于逻辑约束,细粒度约束。对应.qxp文件。design partiong——设计分区

(4)核心频率+时序例外约束+IO约束+LogicLock

LogicLock是粗粒度约束,属于物理约束,FloorPlanning。对应.qsf文件

通过时序约束而不是显式的布局布线约束来达到时序收敛才是时序约束的真谛。

“好的时序是设计出来的,不是约束出来的”在设计是尽量使用时序逻辑避免组合逻辑。