|

����

BEGIN

IF CLK��EVENT AND CLK=��1��

THEN Q1<=D;

END IF;

��������������䣺������������У�û�н����п��ܷ��������������Ӧ�Ĵ�����ʽ��������������VHDL�ۺ�������Ϊ�����ڲ����������������Q1<=D��ִ�У�������Ҫ����ǰһ��ʱ��������ʱQ1�����µ�ֵ���������ֵ�·��˵������һ��ֵ���䣬����Ҫ�õ����д洢���ܵ�Ԫ����������ʱ��Ԫ������Q1��ֵ��

���ò�������������乹��ʱ���·����VHDL����ʱ���·����Ҫ;����ͨ���������������ֻ�ܹ����������·��

���DZ���Ҫע����ǣ���ʹ�����������ƴ���ϵ�·ʱ�����û�г�ֿ��ǵ�·���ܳ��ֵĸ�����������ᵼ�²������������ij��֣��Ӷ��ۺϳ�����߲�ϣ������Ϻ�ʱ���·�Ļ���塣

����˵����

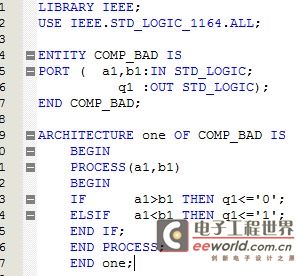

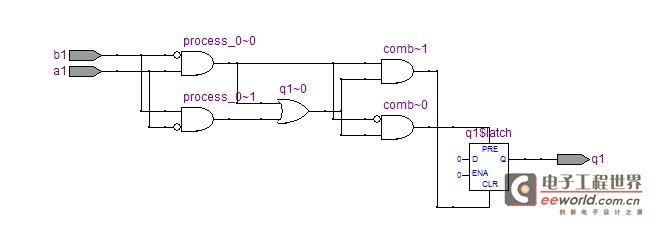

����Ҫ���һ������ϵ�·�Ƚ�������4-1�������������©���˵�a1=b1ʱ���β����ı�������������˲������������ij��֣������ۺ�������Ϊ������a1=b1ʱ�����κθ�ֵ����������q1��ֵ���䣬��Ϊq1����һ���Ĵ��������ǵ�·�б������˲���Ҫ��ʱ��Ԫ�����˷�������Դ�������˵�·�Ĺ����ٶȡ���ͼ4-1

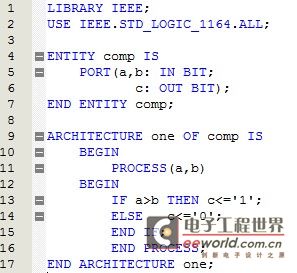

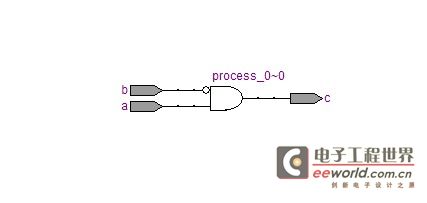

����4-2�Ľ������У�ELSE q1<=��0�� ������a1��b1ʱ��������Ӷ�������ͼ4-2��ʾ�ļ��ĵ�·ͼ��