||

“在开发过程中使用了两片Virtex-5 FPGA(XC5VLX330T)的System Monitor功能,并获得了极大成功。我们的开发板遇到了一种非常少见的问题——当FPGA执行特定功能时,开发板会自动关闭。原因是由于违反了特定的电源阈值规则,电源管理软件将开发板的电源关闭。利用Virtex-5 FPGA System Monitor,可以动态查看这种电源阈值规则违反事件发生的位置,并快速找到解决方案。上述事件的原因最终被确定为:在为FPGA供电的某个稳压器中,开发板供应商发生了简单的阻值计算错误。充分利用这一内置工具,大幅缩短了调试时间,而且不必使用昂贵的调试设备。”

电子设备的功耗和电源系统设计任务变得日趋复杂。静态电流和不断增大的动态电流需求意味着电源分配系统中更大的IR压降。由于工作温度方面的要求,需要采用复杂的散热和通风措施。Virtex®-5 FPGA System Monitor具

备管芯内建温度和电压测量功能,能够为PCB电源设计的开发、评估、调试、优化及合格认证提供有价值的信息。本文介绍了如何配置System Monitor的外部通道来进行电源监控,并提供了一些针对PCB实现的建议和指导。

System Monitor简介

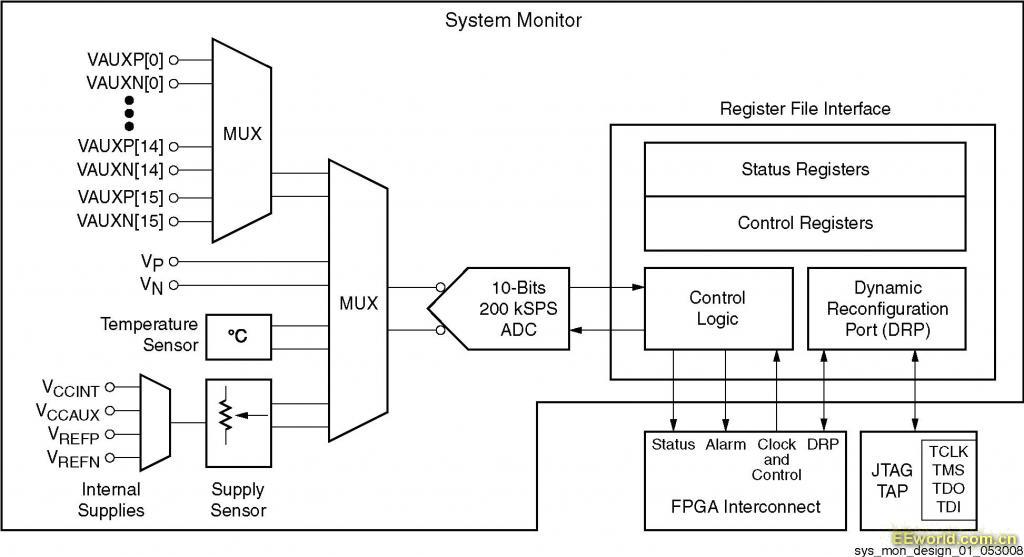

Virtex-5 FPGA System Monitor的核心是一个200 kSPS(20万次采样每秒)的模拟数字转换器(ADC)。图1给出了System Monitor的框图。

System Monitor为访问片上的关键FPGA模拟信息提供了极大的方便。ADC的输入是管芯内建温度和电压传感器。利用其17个外部通道,System Monitor还可以测量PCB或外部封装的物理环境参数。控制逻辑部分实现了常用的自动通道排序、过滤和告警等监控功能。所有这些功能都是用户可编程的,并可以在运行过程中经由动态重配置端口(DRP)通过FPGA逻辑中的寄存器文件接口来定制。DRP是多种Xilinx® FPGA模块中提供的标准总线接口。

该端口支持对特定模块的配置进行动态更新。或者,也可以通过JTAG测试访问端口(TAP),从外部访问寄存器文件接口。事实上,在利用JTAG TAP配置器件前,就可以访问和应用System Monitor功能。

电源验证

随着电流需求的增加而电源电压的降低,提高了对电源系统中阻抗的敏感性,进一步加大了电源系统设计的复杂度。供电电压的降低意味着电源电压的误差裕量更小。也就是说,容差绝对值与电源电压本身成比例。例如,1V VCCINT供电电压的容差指标是±5%或±50mV。对于5A的电流需求、PCB电源系统中仅10 mW (10 micro-ohms ) 的未记串联电阻和标称电压为1V的电源,所传递的电源电压的直流电平就已经达到所规定的下限值(即,当5A电流流经10mW (10 micro-ohms ) PCB阻抗时,在稳压器和Virtex-5器件之间产生50 mV的PCB电压降,因此器件的实际供电电压为0.95V)。

现代BGA形式的封装几乎不可能在器件的焊球上附加物理探针,因此很难确定FPGA的实际供电电平。System Monitor解决了这一问题。片上实际供电电压的精确测量第一次变得可行且易于实现。System Monitor功能集成的内部电压传感器能够以1%的精度对VCCINT和VCCAUX电压进行片上测量。

直接在器件管芯上精确测量出的供电电平为开发工程师提供了用于确定所需电源直流(DC)设置点的关键信息。这避免了因为缺乏对电源和负载间压降的了解而设置过多的裕量。就功耗来说,电源电平的过多裕量代价高昂。静态功耗约与直流电平的立方成正比。动态功耗约与直流电平的平方成正比。例如,直流电平降低2%意味着静态功耗降低约6%,动态功耗降低约4%。

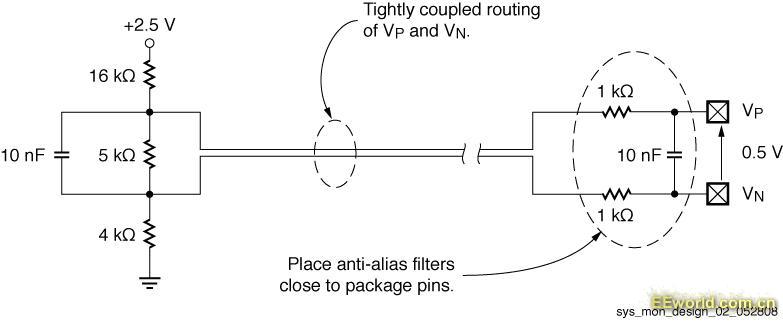

System Monitor的外部通道可用来测量PCB板上其他点的电平。唯一的限制是施加在System Monitor输入上的待测电平必须落在System Monitor规定的输入范围内。利用简单的电阻分压网络可以将大于1V的待测电压衰减到规定的范围内。如图2所示。

图2中,信号被衰减为原有的1/5,再输入到System Monitor进行测量。System Monitor以单极模式测量得到0.5V的电压电平,并返回代表这一电平的代码。然后,将测量结果放大5倍,从而可以得到待测电源电压。

就PCB实现来说,有几点需要注意:

§ 要保证衰减时的精度,电阻分压网络使用的电阻必须精确。

§ 连接到System Monitor输入的布线必须采用紧耦合差分方式实现。保持这些路径紧耦合确保了任何可能的噪声拾取是共模的从而能够被System Monitor的差分模式所抑制。

§ 除了System Monitor输入路径上的其他带宽限制电路以外,必须在其外部模拟输入对上放置一个低通(抗混)滤波器网络,并且应当尽可能靠近器件引脚。这一低通滤波器旨在滤除进入ADC的高频分量,避免测量不可靠。

与所有System Monitor输出一样,这一数据可以通过JTAG TAP读取。可以使用PCB的标准JTAG基础结构设计来确定原型电源系统的完整性,甚至是在FPGA位流最终完成之前。当然,当评估IR压降时,必须在工作电流存在的条件下进行测量。

实时VCCINT电源测量

在系统设计的开发/评估阶段,System Monitor与外部分流电阻相结合可以有效地用于VCCINT电源的测量。测量的具体布置如图3所示。

System Monitor可测量低阻值精确分流电阻两端的电压降(VKELVIN)。利用已知的分流电阻阻值RSHUNT和由System Monitor准确测量的分流电阻两端的电压降VKELVIN,可以确定ICCINT值。对于小于等于1.1V的VP值,上述测量应当以System Monitor双极模式实现。

计算举例

RSHUNT = 10 mW

VKELVIN = 100 mV(由System Monitor测量得到)

VCCINT = 1V(由System Monitor测量得到)

在这个例子中,System Monitor测量出分流电阻两端的电压降为100 mV。

VKELVIN = ICCINTRSHUNT

=> ICCINT = VKELVIN/RSHUNT

=> ICCINT = 100 mV/10 mW

=> ICCINT = 10A

PCCINT = VCCINTICCINT

=> PCCINT = 1V×10A

=> PCCINT = 10W

System Monitor采用一个10位ADC来测量VKELVIN,其相对精度为1位(约相当于全量程的0.1%或1mV)。在上面的例子中,在电流和功率测量中,1mV相当于1%(1 mV/100 mV)。

这里没有讨论通过具有精密电阻的仪表级放大器来预处理VKELVIN信号的其他外部方法,但是也可以采用这些方法来将1mV减小为远小于测量范围的1%。

当在PCB上实现这一传感器时,重要的是通过电源来补偿分流电阻两端的电压降。这样做才能够确保FPGA在其VCCINT输入处接收到正确的电压电平。可以利用电源的传感输入来测量负载点处的VCCINT数值来实现这一点。System Monitor的VCCINT直流电平管芯内建测量信息可以用来确定电源的设置点。

与所有外部测量实现方法一样,System Monitor信号输入布线需采用紧耦合差分方式,并采用抗混滤波器来减小共模噪声源的影响。

利用准确的结温数据估算静态功耗

可以利用外部解决方案来测量结温。例如,热敏二极管监控电路可以提供准确的管芯温度测量数据。然而,这种方案除了需要增加外部监控电路本身以外,还很容易受噪声干扰,并受到其他实施细节的限制,因此实现较为困难。System Monitor的集成温度传感器就避免了这些问题。

System Monitor的集成温度传感器为用户提供了准确的管芯中心结温测量结果。通过FPGA逻辑构造或JTAG TAP可以方便地获取这一数据,在实现了完全无介入测量的同时,还避免了气流干扰或其他环境因素的影响。

能够获知器件结温信息在开发/评估阶段提供了巨大优势。在调试时,监控温度变化和获知设计或系统中发生的事件与异常温度波动之间的时间相关性提供了非常实用的设计工具。在大电流工作期间监控结温度可以快速诊断潜在的问题。

由于各种设计都必须满足功率预算,因此获知实际器件结温对于确定设计的实际功耗至关重要(参考:javascript:;)。通常,在进行功率估计时,并未正确考虑静态功耗与温度之间存在的指数关系。由于不知道实际器件结温,静态功耗估计通常会变得不切实际。许多使用System Monitor的客户都对其设计中所达到的结温感到惊讶。在许多设计中,静态和动态功耗的比例关系接近50/50,因此准确的静态功耗估计非常重要。如图4所示,从环境或外部探测数据来外推/投射结温通常是不太准确的。采用System Monitor可消除这一不确定性。

图4:归一化泄漏电流与器件结温的关系

“一劳永逸”的环境监控

在系统调试或运行时,实现一个环境条件后台监控系统是另一项有用的功能。System Monitor在其内部传感器通道上集成了用户可定制的告警系统。当发生过热或过压/欠压条件时,系统会自动生成告警信号。告警的阈值设置是用户可定义的。告警信号可通过FPGA逻辑访问。此功能的一个简单应用模式是将告警输出信号连接至板上的错误LED。更为复杂的应用模式则是使用处理器控制系统管理解决方案中的告警功能。

环境条件的图形显示

熟悉ChipScope™ Pro调试工具的用户都了解,它直接将逻辑分析仪、总线分析仪或虚拟I/O小巧软件内核插入到设计中来查看内部信号或结点。ChipScope Pro工具也支持对Virtex-5 FPGA System Monitor功能的访问。在ChipScope Pro工具环境内,用户除了可以捕获设计的逻辑状态以外,还可以获得芯片物理环境的图像,根据System Monitor外部通道的使用情况,甚至还可以获得更多参数。在调用ChipScope Pro工具后,ChipScope Pro工具会在JTAG链上自动检测System Monitor是否存在,并提供一个用户控制台来访问其功能。可参看图5。

图5:利用ChipScope Pro通过JTAG访问System Monitor

在缺省模式下,ChipScope Pro工具的System Monitor控制台(图6)将绘制出通过内部传感器测量得到的温度、VCCAUX和VCCINT数据的曲线图表。除了这些数据以外,该控制台还允许用户随时显示任意System Monitor外部通道。ChipScope Pro工具还提供了带时间戳的数据日志功能,以便进一步分析这些测量结果。System Monitor所提供的温度和电压数据在开发、调试和评估阶段极为有用。使用这些资源所需要的设计工作很少或根本不需要任何设计工作。

图6:ChipScope Pro Tool的System Monitor控制台界面

除了绘图和数据日志功能以外,ChipScope Pro工具还可通过JTAG TAP对System Monitor的寄存器文件接口进行完全的读/写访问。这一功能一上电就可以使用。通过ChipScope Pro工具访问System Monitor不需要任何FPGA配置。ChipScope Pro工具界面允许用户对System Monitor的各种功能进行全面的定制。

结论

Virtex-5 FPGA特有的System Monitor功能以最小的设计代价提供了对关键模拟信息的便捷访问。这些数据可以用在开发/原型/评估阶段,为开发工程师提供关于电源系统的重要信息。可以对电源传输系统中的IR压降进行监控,并能够快速确定与电源或PCB实现有关的潜在问题。通过JTAG TAP和ChipScope Pro工具,能够以快速、方便、高效的方式,使用System Monitor的全部功能。System Monitor的温度传感功能可准确测量实际器件的结温,从而可用来更准确地进行实际功耗估算。System Monitor功能配合外部分流电阻可以实现VCCINT电源的功耗测量。

作者:Pádraig Kelly,赛灵思(Xilinx)