请完成以下验证码

||

如何将管脚设置为虚拟管脚

我们在设计子模块时,运行Full Compilation可能会遇到以下两个问题:

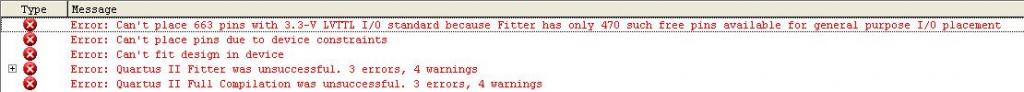

⑴ 子模块使用的I/O太多,FPGA的I/O资源不够分配,如图1所示。

图1 FPGA的I/O资源不够

⑵ Quartus II时序分析时将子模块间的互联当作外部I/O,引起Fmax比实际情况要低。

为了解决这两个问题,通常我们可以将这些管脚设置为虚拟管脚,具体设置方法如下。

⑴ 在Assignment Editor中设置虚拟管脚

打开Assignment Editor,各选项设置如图2所示,To为要设置的I/O,Value要设置为On。

图2 在Assignment Editor中设置Virtual Pin

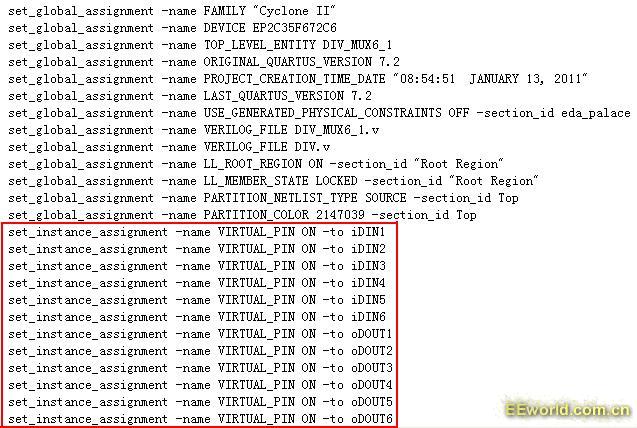

⑵ 在QSF(Quartus Settings File)文件中设置虚拟管脚

Quartus II工程建好后,会自动生成QSF文件,我们通过在QSF文件中加入如下命令来设置虚拟管脚,Set_instance_assignment –name VIRTUAL_PIN ON –to [I/O name]。

图3 在QSF文件中设置Virtual Pin